Arithmetic Logic Unit

The ALU considered carries out four functions:- Addition of two 4-bit numbers.

- Complementing all the bits of a 4-bit vector.

- Bit-by-bit AND operation on two nibbles.

- Bit-by-bit XOR operation on two nibbles.

A set of 2 mode select bits selects the function to be carried out from amongst

the above four. The design has been evolved in a step-by-step manner.

4BIT FULL ADDER

module add4g(sum,carry,a,b,cin);

input[3:0]a,b;

input cin;

output[3:0]sum;

output carry;

wire [2:0]cc;

fa a0(sum[0],cc[0],a[0],b[0],cin);

fa a1(sum[1],cc[1],a[1],b[1],cc[0]);

fa a2(sum[2],cc[2],a[2],b[2],cc[1]);

fa a3(sum[3],carry,a[3],b[3],cc[2]);

endmodule

4BIT-AND

module andg4(c,a,b);

input[3:0]a,b;

output[3:0]c;

and(c[0],a[0],b[0]);

and(c[1],a[1],b[1]);

and(c[2],a[2],b[2]);

and(c[3],a[3],b[3]);

endmodule

4BIT-XOR

module xorg(c,a,b);

input[3:0]a,b;

//input cen;

output[3:0]c;

wire [3:0]cc;

xor x0(c[0],a[0],b[0]);

xor x1(c[1],a[1],b[1]);

xor x2(c[2],a[2],b[2]);

xor x3(c[3],a[3],b[3]);

endmodule

4BIT-NOT

module compl(c,a);

input[3:0]a;

output[3:0]c;

not(c[0],a[0]);

not(c[1],a[1]);

not(c[2],a[2]);

not(c[3],a[3]);

endmodule

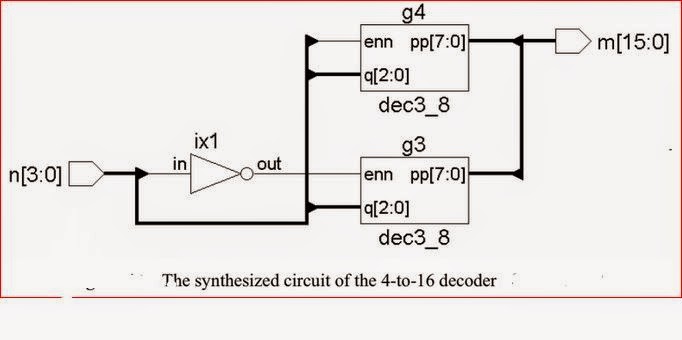

2-4 DECODER

module dec2_4 (a,b,en);

output [3:0] a;

input [1:0]b;

input en;

wire [1:0]bb;

not(bb[1],b[1]),(bb[0],b[0]);

and(a[0],en,bb[1],bb[0]),(a[1],en,bb[1],b[0]),

(a[2],en,b[1],bb[0]),(a[3],en,b[1],b[0]);

endmodule

4-1 MUX

module mux4_1alu(y,i,e);

input [3:0] i;

input e;

output [3:0]y;

bufif1 g1(y[3],i[3],e);

bufif1 g2(y[2],i[2],e);

bufif1 g3(y[1],i[1],e);

bufif1 g4(y[0],i[0],e);

endmodule

ALU module

module alu_4g(a,b,c,carry,cin,cen,s);

input [3:0]a,b;

input[1:0]s;

input cen,cin;

output [3:0]c;

output carry;

wire [3:0] data0,data1,data2,data3,e;

wire carry1 ;

dec2_4 m5(e,s,cen);

add4g m1(data0,carry1,a,b,cin);

compl m2(data1,a);

xorg m3(data2,a,b);

andg4 m4(data3,a,b);

bufif1 g5(carry,carry1,cen);

mux4_1alu m6(c,data0,e[0]);

mux4_1alu m7(c,data1,e[1]);

mux4_1alu m8(c,data2,e[2]);

mux4_1alu m9(c,data3,e[3]);

endmodule