An RS Flip-Flop

module srff(s,r,q,qb);

input s,r;

output q,qb;

wire ss,rr;

not(ss,s),(rr,r);

nand(q,ss,qb);

nand(qb,rr,q);

endmodule

module tstsrff; //test-bench

reg s,r;

wire q,qb;

srff ff(s,r,q,qb);

initial

begin

s =1'b1;

r =1'b0;

end

always

begin

#2 s =1'b0;r =1'b0;

#2 s =1'b0;r =1'b1;

#2 s =1'b0;r =1'b0;

#2 s =1'b1;r =1'b0;

#2 s =1'b0;r =1'b0;

end

initial $monitor($time, " s = %b, r = %b, q = %b, qb = %b ",s,r,q,qb);

initial #20 $stop;

endmodule

Clocked RS Flip-Flop

module srffcplev(cp,s,r,q,qb);

input cp,s,r;

output q,qb;

wire ss,rr;

nand(ss,s,cp),(rr,r,cp),(q,ss,qb),(qb,rr,q);

endmodule

module srffcplev_tst;// test-bench

reg cp,s,r;

wire q,qb;

srffcplev ff(cp,s,r,q,qb);

initial

begin

cp=1'b0;

s =1'b1;

r =1'b0;

end

always #2cp=~cp;

always

begin

#4 s =1'b0;r =1'b0;

#4 s =1'b0;r =1'b1;

#4 s =1'b0;r =1'b0;

#4 s =1'b1;r =1'b0;

#4 s =1'b0;r =1'b0;

end

initial $monitor($time,"cp = %b ,s = %b , r = %b , q = %b , qb = %b " ,cp,s,r,q,qb);

initial #20 $stop;

endmodule

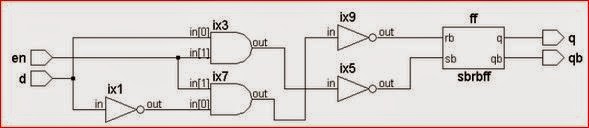

D-Latch

module dlatch(en,d,q,qb);

input d,en;

output q,qb;

wire dd;

wire s,r;

not n1(dd,d);

nand (sb,d,en);

nand g2(rb,dd,en);

sbrbff ff(sb,rb,q,qb);//Instantiation of the sbrbff

endmodule

module tstdlatch; //test-bench

reg d,en;

wire q,qb;

dlatch ff(en,d,q,qb);

initial

begin

d = 1'b0;

en = 1'b0;

end

always #4 en =~en;

always #8 d=~d;

initial $monitor($time," en = %b , d = %b , q = %b , qb= %b " , en,d,q,qb);

initial #40 $stop;

endmodule

No comments:

Post a Comment